Warsaw University of Technology

FACULTY OF ELECTRONICS AND INFORMATION TECHNOLOGY

Institute of Informatics

# Bachelor's diploma thesis

in the field of study Computer Science and specialisation Computer Systems and Networks

FPGA based hardware accelerator for musical synthesis for Linux system

Jakub Duchniewicz

student record book number 277132

thesis supervisor dr hab. inż. Wojciech M. Zabołotny

WARSAW 2020

## FPGA based hardware accelerator for musical synthesis for Linux system

**Abstract.** Work focuses on realizing audio synthesizer in a System on Chip, utilizing FPGA hardware resources. The resulting sound can be polyphonic and can be played directly by an analog connection and is returned to the Hard Processor System running Linux OS. It covers aspects of sound synthesis in hardware and writing Linux Device Drivers for communicating with the FPGA utilizing DMA. An optimal approach to synthesis is researched and assessed and LUT-based interpolation is asserted as the best choice for this project. A novel State Variable IIR Filter is implemented in Verilog and utilized. Four waveforms are synthesized: sine, square, sawtooth and triangle, and their switching can be done instantaneously. A sample mixer capable of spreading the overflowing amplitudes in phase is implemented. Linux Device Driver conforming to the ALSA standard is written and utilized as a soundcard capable of generating the sound of 24 bits precision at 96kHz sampling speed in real time. The system is extended with a simple GPIO analog sound output through 1 pin Sigma-Delta DAC.

Keywords: FPGA, Sound Synthesis, SoC, DMA, SVF

### Sprzętowy syntezator muzyczny wykorzystujący FPGA dla systemu Linux

Streszczenie. Celem pracy jest realizacja syntezatora muzycznego na platformie SoC (System on Chip) z wykorzystaniem zasobów sprzętowych FPGA. Wymagana jest generacja polifonicznego dźwięku, który można odtworzyć w czasie rzeczywistym za pomocą przetwornika cyfrowo analogowego. Wygenerowany dźwięk jest także przekazywany do systemu Linux, pracującego na procesorze systemu SoC. W pracy poruszone są zagadnienia dotyczące sprzętowej syntezy muzycznej, tworzenia sterownika urządzenia dla systemu Linux oraz komunikacji z FPGA poprzez DMA. Po zbadaniu szeregu sposobów syntezy, zostaje wybrany system z interpolacją przy użyciu LUT. Zaprojektowany został nowatorski filtr zmiennych stanu o nieskończonej odpowiedzi impulsowej, który został zaimplementowany w języku Verilog a następnie użyty jako filtr dolnoprzepustowy. Syntezowane są cztery przebiegi akustyczne: sinusoidalny, kwadratowy, piłowy oraz trójkątny. Dla wzbogacenia efektów muzycznych możliwe jest ich błyskawiczne przełaczanie. W celu zminimalizowania zniekształcenia dźwięku przy chwilowym przekroczeniu zakresu podczas sumowania próbek, zrealizowano eksperymentalny akumulator próbek, który rozkłada w czasie próbki o wartości wykraczającej poza zakres reprezentacji wyjściowej. Dzięki temu sterownikowi urządzenie jest widoczne w systemie Linux jako karta dźwiękowa, która jest w pełni zgodna ze standardem ALSA, oraz generuje dźwięk o rozdzielczości 24 bitów z częstotliwością próbkowania 96kHz. System jest rozszerzony za pomocą przetwornika cyfrowo-analogowego zaimplementowanego w układzie Sigma-Delta na jednym bicie GPIO.

Słowa kluczowe: FPGA, Synteza dźwięku, SoC, DMA, SVF

załącznik nr 10 do zarządzenia nr 46 /2016 Rektora PW

miejscowość i data place and date

imię i nazwisko studenta name and surname of the student

numer albumu

student record book number

kierunek studiów field of study

#### **OŚWIADCZENIE**

#### DECLARATION

Świadomy/-a odpowiedzialności karnej za składanie fałszywych zeznań oświadczam, że niniejsza praca dyplomowa została napisana przeze mnie samodzielnie, pod opieką kierującego pracą dyplomową.

Under the penalty of perjury, I hereby certify that I wrote my diploma thesis on my own, under the guidance of the thesis supervisor.

Jednocześnie oświadczam, że: *I also declare that:*

- niniejsza praca dyplomowa nie narusza praw autorskich w rozumieniu ustawy z dnia 4 lutego 1994 roku o prawie autorskim i prawach pokrewnych (Dz.U. z 2006 r. Nr 90, poz. 631 z późn. zm.) oraz dóbr osobistych chronionych prawem cywilnym,

- this diploma thesis does not constitute infringement of copyright following the act of 4 February 1994 on copyright and related rights (Journal of Acts of 2006 no. 90, item 631 with further amendments) or personal rights protected under the civil law,

- niniejsza praca dyplomowa nie zawiera danych i informacji, które uzyskałem/-am w sposób niedozwolony,

- the diploma thesis does not contain data or information acquired in an illegal way,

- niniejsza praca dyplomowa nie była wcześniej podstawą żadnej innej urzędowej procedury związanej z nadawaniem dyplomów lub tytułów zawodowych,

- the diploma thesis has never been the basis of any other official proceedings leading to the award of diplomas or professional degrees,

- wszystkie informacje umieszczone w niniejszej pracy, uzyskane ze źródeł pisanych i elektronicznych, zostały udokumentowane w wykazie literatury odpowiednimi odnośnikami,

- all information included in the diploma thesis, derived from printed and electronic sources, has been documented with relevant references in the literature section,

- znam regulacje prawne Politechniki Warszawskiej w sprawie zarządzania prawami autorskimi i prawami pokrewnymi, prawami własności przemysłowej oraz zasadami komercjalizacji.

- I am aware of the regulations at Warsaw University of Technology on management of copyright and related rights, industrial property rights and commercialisation.

Politechnika Warszawska Warsaw University of Technology

Oświadczam, że treść pracy dyplomowej w wersji drukowanej, treść pracy dyplomowej zawartej na nośniku elektronicznym (płycie kompaktowej) oraz treść pracy dyplomowej w module APD systemu USOS są identyczne.

I certify that the content of the printed version of the diploma thesis, the content of the electronic version of the diploma thesis (on a CD) and the content of the diploma thesis in the Archive of Diploma Theses (APD module) of the USOS system are identical.

.....

czytelny podpis studenta legible signature of the student

## Contents

| 1. | Intro | oduction                         | 9  |

|----|-------|----------------------------------|----|

|    | 1.1.  | Scope of Thesis                  | 9  |

|    | 1.2.  | Thesis Layout                    | 10 |

|    | 1.3.  | Overview of existing solutions   | 10 |

|    |       | 1.3.1. Synthesis techniques      | 10 |

|    |       | 1.3.2. DMA techniques            | 11 |

|    |       | 1.3.3. Writing ALSA driver       | 11 |

| 2. | Back  | <b>cground</b>                   | 12 |

|    | 2.1.  | Origins of synthesis             | 12 |

|    | 2.2.  | Synthesis approaches             | 14 |

|    |       | 2.2.1. Subtractive synthesis     | 14 |

|    |       | 2.2.2. Additive synthesis        | 15 |

|    |       | 2.2.3. Other approaches          | 16 |

|    | 2.3.  | MIDI protocol 1                  | 16 |

| 3. | Harc  | lware overview and System Design | 17 |

|    | 3.1.  | Hardware overview                | 17 |

|    | 3.2.  | Requirements Analysis            | 19 |

|    | 3.3.  | System Design                    | 20 |

| 4. | Harc  | lware Design                     | 21 |

|    | 4.1.  | Sine wave generation             | 22 |

|    | 4.2.  | Square wave generation           | 24 |

|    | 4.3.  | Sawtooth wave generation         | 25 |

|    | 4.4.  | Triangle wave generation         | 25 |

|    | 4.5.  | State Variable Filter            | 25 |

|    | 4.6.  | Sample accumulator               | 26 |

| 5. | Soft  | ware Design                      | 28 |

|    | 5.1.  | Board Setup                      | 29 |

|    | 5.2.  | MIDI receiving application       | 30 |

|    | 5.3.  | DMA - ALSA synthesizer driver 3  | 30 |

|    | 5.4.  | Obtaining the data               | 31 |

| 6. | Testi | ing                              | 32 |

|    | 6.1.  | Verilog Testbenches              | 32 |

|    | 6.2.  | Oscilloscope testing             | 33 |

|    | 6.3.  | System Testing                   | 36 |

|    |       | 6.3.1. Examples                  | 38 |

|    | 6.4.  | Debugging                        | 39 |

|    | 6.5.  | Timing and Delays                | 39 |

|     |        | 6.5.1.     | Software   | e delays | • • • | <br>• | <br>• | ••• | • | <br>• | • • | • | • |       | • | <br>• | • | <br>• | ••• | 39 |

|-----|--------|------------|------------|----------|-------|-------|-------|-----|---|-------|-----|---|---|-------|---|-------|---|-------|-----|----|

|     |        | 6.5.2.     | Hardwar    | e delay  | vs.   | <br>• | <br>• |     | • | <br>• | • • | • | • |       | • | <br>• | • | <br>• | ••• | 39 |

| 7.  | Resu   | ılts       |            |          |       | <br>• |       |     | • | <br>• | • • | • | • |       | • | <br>• | • |       | ••• | 41 |

|     | 7.1.   | Resour     | ce Utiliza | tion .   |       | <br>• | <br>• |     | • | <br>• | • • | • | • | <br>• | • | <br>• | • |       | ••• | 41 |

| 8.  | Con    | clusions   |            |          |       | <br>• | <br>• |     | • | <br>• | • • | • | • | <br>• | • | <br>• | • | <br>• | ••• | 42 |

|     | 8.1.   | Future     | Work       |          |       | <br>• |       |     | • | <br>• | • • | • | • |       | • | <br>• | • | <br>• | ••  | 43 |

|     | 8.2.   | Alterna    | tive solu  | tions    |       | <br>• | <br>• |     | • | <br>• | • • | • | • |       | • | <br>• | • | <br>• | ••• | 44 |

| 9.  | Ackr   | nowledg    | ements     |          |       | <br>• |       |     | • | <br>• | • • | • | • |       | • | <br>• | • |       | ••  | 45 |

| Re  | feren  | <b>ces</b> |            |          |       | <br>• |       |     | • | <br>• | • • | • | • |       | • | <br>• | • | <br>• | ••  | 47 |

| Lis | t of S | ymbols     | and Abb    | reviatio | ons   | <br>• |       |     | • | <br>• | • • | • | • |       | • | <br>• | • | <br>• | ••  | 49 |

| Lis | t of F | igures .   |            |          |       | <br>• |       |     | • | <br>• | • • | • | • |       | • | <br>• | • | <br>• | ••  | 50 |

| Lis | t of A | ppendi     | ces        |          |       | <br>• | <br>• |     | • | <br>• | • • | • | • |       | • | <br>• | • | <br>• |     | 50 |

## 1. Introduction

Since the popularization of a modular one by Robert Moog in the mid-60s, synthesizers have changed the way humans produce music tremendously. While at first analog, they soon became digital and dominated the music industry. Nevertheless, analog ones are still sought for their unique sound and because they can produce signals less deterministic than digital ones.

Because a synthesizer can imitate real instruments it is often used by professional and amateur musicians alike. Such a synthesizer often can be implemented solely in software, but when on-stage and performing live, an artist requires it to be at least partly embedded into the hardware. When realized in hardware, it can be composed of special Digital Signal Processing units, which are designed especially for this. However, for amateur realizations or scientific experiments such a solution is often too inflexible and in such cases implementing this in Programmable Logic is more appropriate. Field Programmable Gate Arrays are the most popular types of such devices, and they allow for very rapid prototyping of a hardware circuit written in a Hardware Description Language such as Verilog, SystemVerilog or VHDL.

The world of FPGA's is constantly evolving and the available materials soon become obsolete and the developer has to face a plethora of time-consuming challenges. Apart from them, they have to possess knowledge ranging from electronic circuit design, through digital and analog filtering knowledge, to Linux Device Drivers and Linux internals understanding. For this project especially, understanding signal processing was crucial because it utilizes a Numerically Controlled Oscillator for the waveform generation. Moreover, some degree of proficiency with high-speed digital circuits was required to implement PL pipelining.

#### 1.1. Scope of Thesis

This project is meant to utilize System on a Chip that comprises FPGA to generate signals corresponding to a MIDI note read from the user, and process them in Hardware, before passing them to Software running a Linux Operating System. The combination of HPS and FPGA is desired because it allows for utilizing best of both worlds, parrallelism of the FPGA paired with the potential of the Linux on top of the HPS. Minimal requirement is a polyphonic sine wave oscillator capable of generating all MIDI notes. While various steps of the sound synthesis and processing may be offloaded to the FPGA to utilize its inherent parallelism, at least a minimal synthesizer should be implemented entirely in PL and then feed that sound to the Linux System via Direct Memory Access. After successful implementation of a sine wave synthesizer different waveforms can be added to even further push the boundaries of this SoC and provide more control to the user.

All the basic processing tasks needed to generate a sound successfully should be

offloaded to the FPGA, while still allowing for the reception of the sound on the Software side and further processing of received signal samples. Hence, generation, filtering and all of the other calculations which can be parallelized should be implemented in the PL while allowing the user to provide their DSP subsystems on the Linux side via the JACK audio system. The data received by the Linux side can be processed in real time or saved to a file. Saving to a file should be without any glitches or unwanted audible effects.

#### 1.2. Thesis Layout

The next chapters of this thesis focus on first introducing concepts and history of sound synthesis, then briefly presenting the MIDI protocol. Next, overall system design is discussed, hardware choice and capabilities are explained, then the functional requirements of the system are stated. Last but not least, both the hardware and the software part are discussed in detail. Communication, synthesis, and effects generation is explained; some details and encountered problems are examined. Finally, testing and results are presented along with an overview of things that were enhanced after thorough testing of the system. The thesis is surmounted with a conclusion and acknowledgments.

#### 1.3. Overview of existing solutions

The topic of creating a synthesizer using Programmable Logic is not one of much widespread eminence. Although various amateur projects are focusing on creating a working synthesizer, almost none of them try to make use of both the hardware and software parts to generate and process the sound. Three main components are usually discussed in scientific papers: synthesis techniques using the FPGA, DMA techniques, and writing an ALSA driver. On the day of writing this thesis, several projects are focusing on utilizing FPGA's for accelerating sound processing. However, none of them implements a working live stand-alone synthesizer which can be further enhanced on the software side.

At the time of writing this article, there seems to be just one work resembling mine. Two students of Worcester Polytechnic implemented synthesizer which utilized FPGA as the main synthesis and effects generator unit while offering Python GUI to the user.[1] The FPGA used there is much more powerful than the one I used in my project, however, was not pushed to the limit. The FPGA used in the cited project was also realized in a SoC system but utilizing the system just for reading the MIDI commands from the external keyboard. It is worth mentioning the extent to which their work implemented various musical effects, most of which are too expensive in terms of resources utilized for my choice of hardware.

#### 1.3.1. Synthesis techniques

This topic is by far the most explored, as it is quite mature and the demand for efficient synthesis techniques is ever-growing. Numerous works focus solely on the ways the

FPGA may be used to accelerate the synthesis process, or where it is used as a standalone synthesizer from the bottom-up. A work by Jacek Borko et al.[2] focuses on the parametric additive synthesis of audio signals while maintaining a low power consumption. Other works solely utilize the FPGA for generating audio effects[3] or make use of the parallelism of the FPGA for converting mono sound on the input to a stereo on output.[4] There are also some course works focusing on teaching some aspects of the FPGA utilization and programming which present interesting approaches to the synthesis. One of such works is a project specification for a project at University of California at Berkeley, where wavetables with precalculated waveforms are sampled using the FPGA to generate sound.[5]

#### 1.3.2. DMA techniques

Utilizing Direct Memory Access is ubiquitous is every high-speed data acquisition or processing system. Because of that numerous works are written on this topic, and it is incessantly developed. One such work presents several distinct techniques for such communication, among which one utilizes DDR as temporary buffers.[6] Because currently, effective utilization of Graphics Processing Units is a popular topic, many works are written regarding FPGA-GPU communication. Thankfully, many complex IP cores have been already written and tested, in turn allowing for robust and quick development of such a solution on the FPGA. One example of such IP core is the Altera mSGDMA IP Core which is documented in the manual[7] and additionally in a guide written by one of the users.[8]

#### 1.3.3. Writing ALSA driver

This last subject is most poorly documented, offering outdated technical guides and almost no scientific work regarding it. Usually, ALSA device drivers are written by specialists, and judging by the scarce amount of such drivers in the Linux kernel git repository, virtually nobody needs to share this knowledge as every device has its specification. Nevertheless, there were some approaches for making it accessible[9], and detailed as this article is, it still leaves out a lot of crucial information. Some of it is complemented with the pages from the ALSA-project wiki page[10] and some of it has to be garnered by trial and error, or reading ALSA source code. Fortunately, there is a project which tried to even further formalize the steps required for writing a successful ALSA driver, but it again failed to convey the most crucial step - data transfer constraints when communicating with real devices.[11][12] Still, it remains the most up-to-date and relevant document regarding ALSA driver implementation and deserves more praise.

## 2. Background

Since the dawning of the human race, music was an indispensable part of our lives. Much can be said about the effects it has on human beings, ranging from motivating and energizing to relaxing and unwinding. The virtue of synthesizers is that they allow generating almost every conceivable sound a human being is capable of hearing, or even beyond that. Because of that, they are nowadays ubiquitous, being embedded in our mobile phones or even in smartwatches. Nevertheless, industry-grade synthesizers are still expensive enough to discourage their compulsive purchase and are a mix of both analog and digital domains.

Because their usage often does not require much specialized domain knowledge beyond some prior musical education, they found their way to almost every household in the form of a musical keyboard. Probably most of the young people were in touch with them at some point in their lives, and some of them use it daily. Synthesizers are an indispensable tool for amateur musicians and music producers because they allow for a broad range of instruments and effects for a low cost. Pairing them with a Digital Audio Workstation permits for enhancing their capabilities and even altering their primary functionality by reprogramming them. Such options are enabled in this project's Novation LaunchKey MINI, where every knob and touchpad can be reprogrammed on a whim of the potential user. Often buying a synthesizer is a much better choice for an amateur musician or a band than buying a specific physical instrument, especially when their theme music is related to electronic or techno. Their current fidelity is such high that sometimes one cannot tell the difference whether the instrument currently being played is generated by means of a synthesizer or a true musical instrument. Nowadays, there is a trend for returning to the origins of synthesis and the craftsmanship of analog synthesizers is abound. This project is somewhat a movement in this direction since it aims to show that sound synthesis is possible in yet another way on yet another hardware and software.

It leaves no doubt that synthesizers changed and improved the ways people create music, facilitating this process as a whole and most importantly allowing for very quick iterations resembling prototyping. Having an abundance of effects and sound banks, one can quickly find a sound that suits them without the need for re-tuning the instrument or even worse ordering a new one to be crafted by a specialist maker. With synthesizers, it takes just one knob turn or one keypress to change the whole sound domain in which the musician currently operates, which makes them much sought after item.

#### 2.1. Origins of synthesis

It is transparent that with the passage of time people would become gradually interested in making the process of sound creation easier and more accessible in both financial terms and certain required skills. The popularization of electricity even further influenced their rapid development. First in form of Theremin[13], Mellotron[14], and then Hammond's Organ[15], synthesizers soon became very popular throughout avant-garde music communities. The de-facto first synthesizer was conceived by Harry Olson and Herber Belar at the RCA laboratories in Princeton in 1957 - RCA Mark II. Because transistors were just being started to be mass-produced, it utilized 750 vacuum tubes instead of them. The next milestone in their development was the creation of a modular synthesizer by Robert Moog, who was an engineer and a physicist. It is worth noting that these synthesizers were all monophonic, and even though they offered various effects to the user, they could be just applied to the single sound being played. Only in 1978, with the release of Prophet-5 from Sequential Circuits, polyphony found its way to the synthesizer world. Moreover, it allowed for storing the sound for future replay, instead of tediously recreating it each time it was desired. Miniaturization of synthesizers was also a popular topic during these times

Figure 2.1. A Minimoog analog synthesizer.

- Minimoog was one of such creations and it is visible in figure 2.1.

By the 1980s, with the rise of MIDI and the conception of first digital synthesizers, they conquered the music market. Pop artists started using them for their performances which greatly influenced their reach. The most popular synthesizer models, being sold even today were developed during this time. Such creations as Yamaha DX7, Roland D-50, or the famous Korg M1 remain prominent examples of precursor digital synthesizers. In the subsequent years, synthesizers became miniaturized and even embedded in special DSP chips that we can find in almost every electronic device. With the passage of time, analog synthesizers became again sought after due to their vintage sound and feel, and probably in search of sounds different from these popular nowadays.

#### 2. Background

It cannot be settled whether it was the synthesizer that made bands like Pink Floyd or musicians such as David Bowie or Jean Michel Jarre popular, or it was the other way round. Nevertheless, they soon became indispensable mediums for progressive rock bands and after a few decades, the groundwork for electronic and techno music. Ranging from classical music, through pop and rock music, to electronic and hard techno, synthesizers have found their way to the contemporary musician and are now an indispensable tool of the trade. If not for them, some greatest musical pieces would not have been composed due to not having such types of sounds to choose from.

#### 2.2. Synthesis approaches

While there are multiple ways to manage sound synthesis, the most prominent of them are a subtractive and additive synthesis. These two are historically the most important ways of achieving the goal of synthesis - generating an audible effect. Some other types include Frequency Modulation synthesis, Sample-Based synthesis, and Granular Synthesis. All of these do not stem from the idea of harmonics and periodicity, but instead, employ different techniques to achieve the same result.

When implementing signal synthesis in the digital domain, one has to take into account that the digital representation is inherently finite when compared to its analog form. Because of that, some special techniques have to be undertaken in order to preserve the highest accuracy and quality of the output signal. The most prominent of which is the concept of Direct Digital Synthesis, which is used in this project extensively.[16]

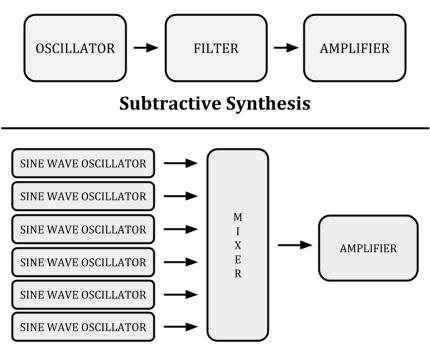

#### 2.2.1. Subtractive synthesis

This is the type of synthesis that was most popular in analog synthesizers because it relies on just two components - harmonic-rich wave generator and a voltage-controlled LPF, the result of these can be then amplified and put through a mixer to achieve polyphony. The most popular wave shapes that are utilized in such synthesize are square, sawtooth, or triangle wave. These of course can be mixed to create even more unique and peculiar results at the final stage of synthesis. The lowpass filter may be a regular one or equipped with a resonance near the cutoff frequency to enhance the resultant sound. Of course, different types of filters may be also applied to filter out for example some special bands or notches in the spectrum. Filters used are usually 2-pole or 4-pole, meaning they have an attenuation of respectively 12 dB or 24 dB per octave. The signal leaving the filter can now be shaped using a special envelope or a simple amplifier. The most popular technique of shaping the envelope is called ADSR which stands for Attack Decay Sustain Release. With these parameters, one can control how long the sound rises, falls, is stable, and finally how long it takes until it disappears after the note is released. Finally, if one desires so they may add a Low Frequency Oscillator to create a vibrato or a sweep effect at the output of the synthesizer. In the end, the signal may be mixed with other signals for polyphonic

output. Wielding all these components, the synthesizer is powerful enough to meet the requirements of even the most demanding musicians.

#### 2.2.2. Additive synthesis

Additive synthesis techniques can be traced back as far as the conception of harmonic wave analysis by Joseph Fourier in 1822. It states that every waveform can be composed of simple harmonic waveforms of different frequencies and is the groundwork behind some of today's most prominent technological advancements such as MRI or space exploration. It can be seen in the figure 2.2. The earliest synthesizers relied on this technique to gener-

**Additive Synthesis**

Figure 2.2. The difference between subtractive and additive synthesis techniques.

ate their unique sounds, such as the Hammond's Organ. In principle, the sinewaves of differing frequencies are mixed to achieve a waveform of much different timbre and shape. Such waveforms as square, triangle, or sawtooth are composed of multiple harmonics of a sinewave, hence they themselves are already results of additive synthesis. Similarly to the subtractive synthesizer, this one also makes use of contour generators and amplifiers to create its myriad sounds. A mixer is used here for every single monophonic sound in order to stack the harmonic waveforms on top of each other. One crucial component of the additive synthesizer is the noise generator, which makes some sounds (especially orchestral ones) sound more real. It is also a building block for a technique called resynthesis, which takes an input sound and tries to recreate the harmonic structure of it.

#### 2.2.3. Other approaches

Apart from the two most popular types of synthesis, some additional are quite popular in the music industry. Frequency Modulation synthesis is one such technique, where via the usage of a modulator oscillator, the frequency of the original wave is changed to produce yet another one. The most prominent example of a synthesizer employing it was Yamaha DX7, which shaped the sound of the 1980s. This concept is fairly similar to the ordinary Frequency Modulation known from radio communication, except here the carrier modulation is in the audible range and allows for interesting results.

On the other hand, sample-based synthesis or wavetable synthesis is based on storing short parts of a periodic signal and running through them with either a slower or a faster pace to generate sounds of differing frequencies. They can be overlapped and combined in any desired way to create novel sound forms. This project utilizes a similar approach to generate the sound, with a quarter-sine wavetable and different tuning words that regulate the output sound frequency.

Granular synthesizers are an upgraded version of the sample-based ones. Their samples are even shorter, around 10-50ms of duration and they are incessantly combined in order to create a fine-grained waveform. They require quite a lot of processing power because of this and with the development of more advanced software, they were adapted in form of programming languages. Starting from mostly console-style ones like CSound, Chuck or Faust through more interactive sorts of Pure Data or SuperCollider, numerous languages have off-sprung from that synthesis technique. Most of them do not require much programming knowledge, and allow for achieving quick effects without real synthesizer hardware. Instead they utilize mostly the software resources of one's PC in conjunction with their soundcard.

#### 2.3. MIDI protocol

Musical Instrument Digital Interface is a protocol used by all modern digital music devices, Digital Audio Workstations, and regular computers. It is important to understand that MIDI is not a musical file format, it is just a sequence of commands that MIDI-compliant devices can interpret and react to. Since 1983 it is an industry-standard protocol for all Musical devices. In 2020 MIDI 2.0 was introduced and brought some new capabilities like profile configuration, property exchange, and protocol negotiation. Because this protocol is still in its infancy, this project utilizes the older version of the protocol. There is also an alternative protocol called Open Sound Control, which is similar to MIDI but allegedly allows for more data types and utilizing symbolic paths instead of numerical addresses of the devices.

MIDI, as a set of commands sent from the generating device to the MIDI-compliant playback device, is utilizing commands encoded in a binary format. Each command is composed of three bytes, the first one being the control byte and the remaining two being the parameter bytes. All bytes except the first one have 0 as MSB, effectively allowing up to 128 values to be set. The first byte informs the receiver what type of message is being sent and to which channel. It is worth noting that MIDI allows up to 16 channels - simultaneous instrument tracks. The two following bytes have a different meaning depending on the context in which they are sent. For note messages, they are consequently: the MIDI value of the note being turned on or off, and the velocity with which it should be played - loudness. For control messages: the controller number and the value assigned to the controller. There is also a pitch/bend sequence of bytes which is used for varying the pitch of currently pressed (or echoing) sound.[17]

## 3. Hardware overview and System Design

Choosing hardware and planning the overall system design is often a demanding task, especially for a project rooted in several distinct fields of study as this. One cannot underline the importance of proper platform choice which often heavily influences the pace at which the project progresses.

#### 3.1. Hardware overview

For the project discussed, I needed a device that would offer both an FPGA and an embedded Linux system with preferably shared memory to make DMA transfers easier. Although there are various devices that offer both FPGA and a HPS capable of running Linux, I was constrained by budget and did not want to spend too much on a board which I would use just once if it turned out not suiting my liking. The obvious choice of the manufacturer arose: Xilinx or Intel. Both offered similar devices at a similar price: De0-Nano-SoC from Intel and slightly more expensive PYNQ-Z2 from Xilinx. The choice was not straightforward, as from a perspective PYNQ offered much more DSP slices which are crucial for my application and the Vivado suite is mostly error-free and allows for the rapid development of prototypes thanks to the broad library of University Programme IP Cores. The lack of rapid-recompile option in the free version of the program is most vexing because in this project compilation times took about 15 minutes, which when debugging a minor issue occurring only on hardware is quite much.

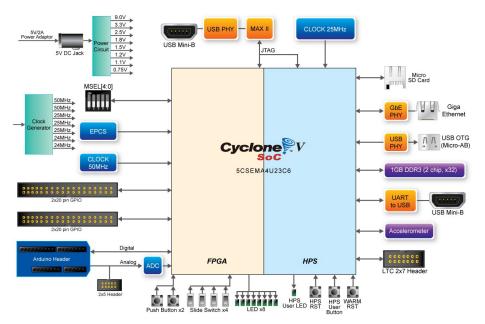

However, after reading numerous reviews and browsing through projects utilizing both of these boards I decided to opt for De0-Nano-SoC. Despite multiple issues with setting up the Quartus IDE, and missing or outdated quickstart's for SoC applications, I was able to quite quickly complete a mock project and blink a LED on it. The board chosen for this project is visible in figure 3.1.

The board features an Altera Cyclone V FPGA with over 20 000 logic elements, 4 Phase Locked Loops and 3 clocks. Moreover it provides the user with a HPS based on ARM

Figure 3.1. De0-Nano-SoC development board

Figure 3.2. Schematic of the De0-Nano-SoC development board

Cortex-A9 Dual-Core processor working at 925MHz and 1GB DDR3 SDRAM which can be shared with the FPGA. It also provides some basic connections: GPIO's, Ethernet, USB connections and push-buttons. It can be visible in figure 3.2.

De0-Nano-SoC can be reconfigured by special settings of MSEL pins to utilize only FPGA, HPS, or both of them simultaneously. The on-board processor is capable of running any embedded Linux distribution, be it Yocto or custom Buildroot setup. It can also support other operating systems, such as FreeRTOS. Overall, the board faced the challenge intrepidly and with some struggling all necessary components could fit into the restricted LE pool, which was much smaller than one in similar projects.

Figure 3.3. Novation Launchkey MINI keyboard

Moreover, for the MIDI compliant device, I have chosen the Launchkey MINI from Novation. It features 25-keys and allows tuning a few octaves up and down, effectively covering the whole MIDI range. It also supports note velocity detection allowing for taking this into account when synthesizing the requested sound. Moreover, it features up to 16 MIDI channels, hence it can act as multiple MIDI instruments at once. Several programmable knobs are also available, for example for pitch-bend control. It can be seen in Figure 3.3

#### 3.2. Requirements Analysis

The system was designed in a particular task in mind: synthesizing a musical signal with the help of the FPGA and outputting the result to the Linux system running on the target. The user is presumably a musician or a hobbyist who would like to have a handy basic synthesizer capable of generating a requested musical note. Once the system is designed and flashed it would require minimal (if any) interaction from the layman user. The system can be extended with additional effects the user would like to implement themselves both in hardware and in software.

Apart from being simply generated, the signal has to be properly filtered by the use of a Low-Pass Filter. The device should allow for a polyphonic playback of requested notes, up to 10 simultaneously. Key presses and releases should be registered without any delay. The resulting sound can be recorded or routed to other applications on the user side in the Linux operating system. Additionally switching between different waveforms should be possible and accessible for the user - preferably in a form of keyboard control push-button or knob.

There should be no audible delays between the keypress and its reception by the human ear. The system should strive for an as pure signal as possible, taking into account distortions incurred by imperfect passive components of the RC circuit.

#### 3.3. System Design

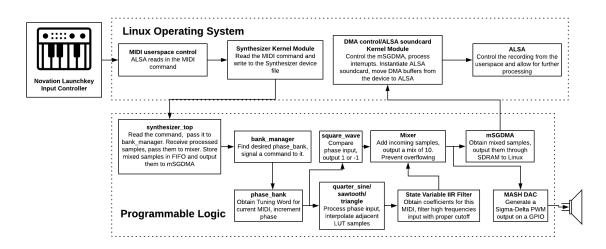

From an overview, the system is composed of just a single board that comprises various distinct components. One such component is the FPGA which is responsible for signal generation, filtering, accumulating polyphonic samples, and passing them via DMA to the Linux OS. Because one of the project requirements is to allow for polyphonic sound generation, an important design decision had to be undertaken - how to generate multiple samples simultaneously. Obviously generating a separate synthesis lane for each of the 10 samples would be too costly, therefore a pipelined approach was conceived. Thus, a multi-cycle penalty is incurred, but since the sampling speed is much lower than the generating speed it is not a problem at all. The hardware side generates and stores the samples for the DMA transfers to the device driver implemented in software and at the same time outputs this generated sound to the delta-sigma DAC [18]. Generated Pulse Width Modulated signal leaves the board via 1 GPIO pin to a second order RC circuit. This allows us to immediately test the signal and observe any issues on an oscilloscope.

On the other hand, the Software part is tasked with reading the MIDI command from the user keyboard device, decoding it and sending an appropriate instruction to the FPGA. Moreover, the software part is responsible for communicating with the mSGDMA device implemented in the FPGA and receiving the buffers. A special ALSA sound-card is emulated by a device driver that receives the buffers via the DMA and feeds them to the ALSA system at appropriate intervals. This device can be used by, for instance, the JACK audio system[19] to even further extend the sound generation and processing pipeline.

A high-level overview of the system is visible in the figure 3.4.

Figure 3.4. High-level overview of the system.

## 4. Hardware Design

The crucial part of the system - the signal generator is implemented in PL on the FPGA. Since DDS requires LUTs, FPGA was an ideal choice of architecture for this project. Moreover, because all DSP blocks usually run in a pipelined fashion, they share resources that otherwise would have to be copied for every additional DDS lane. This project allows for parallel processing of 10 sounds, but this requirement is purely based on the fact that humans usually do not play more than this number of notes simultaneously. The hardware clock runs at 100MHz, while the outputting sampling speed is only 96kHz, and usually no greater is needed for even high-quality sound processing. This allows for many-cycle delays between the sound is generated and actually played back. It is a convenience that is often utilized in projects such as this. Where the clock domains need to be crossed, a double-clocked FIFO IP core block is used, thus eliminating any glitches due to metastability issues. Unfortunately, the slow clock could not be generated using a DLL because there are not enough resources left to do so - its frequency is 96 kHz which would require fractional pipelined DLL's, and these are costly. Hence, the slow clock was implemented using a regular counter and a clock-enable signal which lasts just for a cycle of the fast clock. Because of this approach, Clock Domain Crossing was avoided, which is a common malady when designing logic systems and requires for example double latching and other synchronization mechanisms which deal with Metastability.

From a high-level overview, the system is an NCO with a preprocessing step, an IIR filter, an accumulator, and a sampling module. When the control is issued by the Linux kernel module, which inputs a control message to either play or stop a given note with a velocity corresponding to the force with which it was stricken, the 'synthesizer\_top' module receives it via the Avalon-MM interface and signals the 'bank\_manager' module which then handles its contents. The Bank Manager is tasked with marking which modules

are currently in use and which are free, additionally, it passes all intermediate results along the synthesis chain, such as sine LUT output to the IIR filter. When the signal is finally generated and filtered, it is the Bank Manager, that outputs this result. Handling this data by the Avalon-ST source is done in the top module of the Synthesizer IP Core, which in turn can be either output to a delta-sigma DAC or to the Linux OS running on the target. For outputting the signal to the OS, an mSGDMA IP core is used, which is then controlled on the software side by a Linux Device Driver.

The wave-changing logic is also implemented in the 'bank\_manager' module, where it changes the currently output waveform instantly. There may be a few cycle residue in the SVF because of that but it is unnoticeable by the human ear.

Figure 4.1. A view of pipelining.

The pipelining approach can be seen in the figure 4.1, T is the current sample, T-1 and T+1 are previous and next samples respectively. It can be observed that every pipeline element is constantly working even if the data is not valid in order to maintain pipelining efficiency.

#### 4.1. Sine wave generation

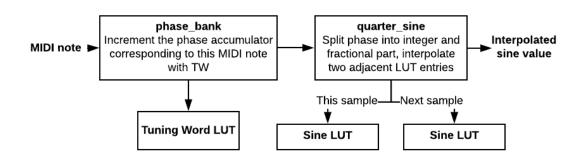

The core of every synthesis - generator is implemented in a way facilitating both resource usage and ease of modification. This generation scheme is visible in 4.2. The

Figure 4.2. Sine generation overview.

groundwork behind such a solution is a phase accumulator and a phase step - the Tuning Word. This tuning word is also obtained from a LUT covering phase increments corresponding to the desired MIDI note. The equation describing the mapping of MIDI note to the frequency is [20]

$$f_{note} = 2^{\frac{(m-69)}{12}} 440 \tag{1}$$

. These Tuning Words are pregenerated with a python script which takes into account the necessary output width, the sampling speed, and the desired frequency of the output signal. Again, the relation adheres to a certain mathematical relation

$$tw = \frac{f_{midi} * 2^{tw_{bits}}}{f_s} \tag{2}$$

. This allows for a flexible stepping through the sine wave LUT for each of the MIDI notes at a low memory cost of just 128 - 24-bit values in case of my solution. Since there are ten phase banks that are stepped through 1-by-1, the effective generator frequency for each of them is 10MHz instead of 100MHz, i.e. they are incremented one in ten cycles of the fast clock. It is important to note that the note sampling frequency has to be specified in the tuning word calculation - 96kHz in this case. The phase counter is an unsigned register of 24-bits of width, therefore it naturally overflows which is the desired effect when implementing a DDS system. The resulting phase is then passed to the sine module, which does the rest of the generation utilizing a sine LUT. It is of course possible to have much greater precision of Tuning Words but this requires a bigger phase register and some changes in the sine generation module, therefore it was unfeasible to further increase its size once 24-bits proved to be enough.

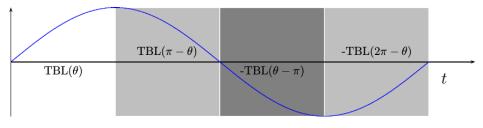

The sine LUTs are of the size of the first quarter of a full sine period because it is a twofold symmetric function and can be easily generated with just a quarter of a period of values at hand. This does not mean such a trade-off is without its consequences - the whole system is delayed by three cycles only due to the sine wave generation and interpretation of the input phase. The diagram explaining the above symmetry is visible in

Figure 4.3. Sine wave symmetry.

4.3. The first symmetry can be observed along with the MSB - the negative symmetry. The second one is the 2nd MSB, which is the rise-fall symmetry, which even further reduces the size of the required LUT. [21] In order to prevent minor glitches in the sine wave size, it is shifted left by 1 sample. In effect, two bits of the incoming phase are utilized just for the symmetry resolution which allows for the generation of a smaller LUT by an order of 4.

Such a solution is quite common in both simple and advanced synthesis systems, because utilizing floating point mathematical functions is often quite costly and in some cases impossible to implement on hardware. If one wished for even greater performance, they could use CORDIC [22], which even further reduces resource utilization on a system like the FPGA.

Initially, such a solution was enough to generate a high-quality, smooth sine wave on output. However, the resource requirement for a high-quality audio wave is huge, assuming just the 16 bits of phase input to this LUT. Obviously, storing a LUT of the size of  $2^{24}$  is unfeasible, as it would occupy much precious LE's which can be used for much more robust tasks. Because of that, a less resource-heavy way of generating sine wave samples was sought and implemented - linear interpolation of the accumulated phase between two adjacent sine wave LUT entries. It comprises two sine LUTs which are then interpolated at a step of 8192 units to attain the 24-bit precision of the whole system. The interpolation is linear, hence previous and next samples are multiplied by the distances from the current phase value. The results of this multiplication are added and they are the resultant sine value. Though this step requires an additional block of multipliers and a cycle is lost to compute the result, it is much more resource-efficient than the approach without interpolation.

Measuring these two distinct generation ways yielded different Signal to Noise Ratios, hinting at the interpolation's superiority. Because the digital quality of the generated sound is more important than the analog one, moreover the analog DAC is not meant to produce the highest possible quality, the SNR is defined for the digital fixed-point integers as follows

$$SNR_{dB} = 20 * \log_{10} \frac{signal_{lvl}}{noise_{lvl}}$$

(3)

The non-interpolated signal achieved the SNR of slightly less than 60dB and the interpolated over 75dB which is a not bad result for taking into account the non-ideality of the interpolation technique. Hence, the interpolation technique in this case proved to be superior to the other in terms of both resultant signal and resource utilization.

#### 4.2. Square wave generation

The square wave is generated without the help of any LUT as it would be non-efficient in terms of resource utilization. Instead, it compares the input phase against a constant representing half of the phase and outputs either a logical -1 or 1 represented by the 2's complement 24-bit value of the corresponding magnitude. Because it is a square-wave and is composed of many periodic signals, the SVF exploited some unexpected behavior with overflows and this signal bypasses the filtering stage. The output signal is arithmetically shifted right by one to equal its magnitude to other signals, like sine or sawtooth.

#### 4.3. Sawtooth wave generation

Similarly to the sine and triangle waves, this waveform uses a LUT for its sample generation. Instead of a quarter-wave, it utilizes a half period LUT which is shifted up for the second part of its period. Instead of 512 LUT entries, twice as that is used to obtain the exact same precision as for other waveforms. The usual 4-cycle latency is also maintained here.

#### 4.4. Triangle wave generation

This waveform is implemented in exactly the same way as the sine wave, except for the LUT which is a rising slope. Again it is only a quarter of wave which is then used twice for interpolation and is outputted after 4 cycles.

#### 4.5. State Variable Filter

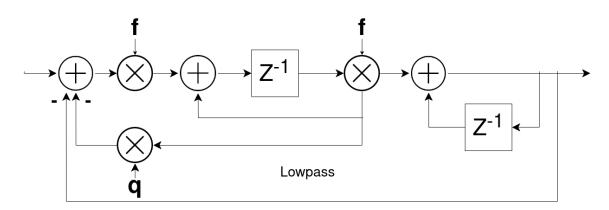

As much as important as the generator, this module is especially vital in an audio signal generation because of high sampling speed and quite low frequencies of the generated signal. The LPF prevents aliasing and harmonic occurrences of the generated signal, therefore making it an ideal candidate for this type of solution. Moreover, this particular type of filter boasts its variable cutoff frequency, which makes it an even better candidate for filtering out all unwanted frequency components depending on the MIDI note stricken. If this was an analog synthesizer, such filters as an ordinary transistor-ladder in a Moog style or a Sallen-Key filter would be a perfect choice. But since this is a digital synthesis project, a different solution is necessary, and thankfully DSP and Audio companies incessantly develop new types and variations of digital filters. What is more, since such filters usually are used in embedded solutions and special DSP processors, they are highly optimized and come in many types.

Initially, such a filter was conceived by Hal Chamberlin and was named a state-variable filter [23], and even though it was an excellent filter implementation back then, it had one galling trait - limited frequency control range. Hopefully, recently Andrew Simper from Cytomic developed a filter based on it which used trapezoidal integration to overcome the aforementioned issue [24]. Implementing this filter in Verilog proved to be challenging for me, as this was the first time I developed a digital filter in this language and for an FPGA.

The filter coefficients were precalculated with a python script as usual and placed in a LUT in a Q2.37 notation because of high precision requirements. This extended precision is maintained throughout whole filter calculations and is truncated only for filter output in order to maintain as much stability and accuracy as possible. This LUT is also not very large in size, and although it could be replaced with an in-system multiplication and division, it would incur unwanted delays and probably a precision loss. For this module, four multipliers are needed to be synthesized and they run in a pipelined fashion like the rest of this project. In just three cycles, the input signal is filtered and is available for

output, which is much faster than it would be possible with the fastest FIR filter. In my implementation, I used the abbreviations in step with these of Andrew's to make it more accessible to a potential reader or implementer.

It is important to note that when numbers are expressed in the Q format, they require special scaling for bringing them back to the ordinary binary notation. For the multiplication result, this scaling has to be performed twice - once for each multiplicand. Forgetting to do so will result in a totally jumbled output signal and a faulty filter. When truncating the output signal, special care needs to be taken in maintaining the sign of this result. Therefore, the MSB and bits from 36 to 14 inclusive are taken as the output signal. This way two bits which are necessary for a precise calculation of fixed-point numbers are skipped and the result is correct.

Figure 4.4. A Lowpass State Variable Filter block diagram.

A diagram showing this particular SVF operation is visible in figure 4.4.

#### 4.6. Sample accumulator

When the sample is finally generated and filtered, it is sent to the sample accumulator which is tasked with mixing the incoming samples from up to 10 synthesis lanes and outputting the result to the FIFO. In order to prevent overflowing of the value, several measures are undertaken and implemented. First of all, the incoming value is scaled down by half by a single arithmetic shift right. Next, when the incoming values are added together, they are compared against MIN and MAX value possible to achieve with signed 24 bits signals, and if after summing they are greater, the overflow buffer is filled with the overflowed amount. The overflow buffer is appropriately sized, to prevent even further overflows and it is unloaded whenever possible. If in one cycle the value starts to overflow and in the next, it is decreasing, the overflow buffer is gradually discharged, until it is empty and the output value is again equal to the actual sum of the inputs. This solution incurs a slight phase delay but prevents loss of precision which is crucial in high-resolution systems like this.

Because it works on a 10-cycle basis, the last cycle has to be treated slightly differently and the code for this is therefore lengthy. To achieve slightly less precision with a simpler implementation, one could ignore more than one cycle of phase delay and just output as much of the overflow buffer in the sample succeeding the overflowed one, ignoring the rest and clearing the overflow register immediately.

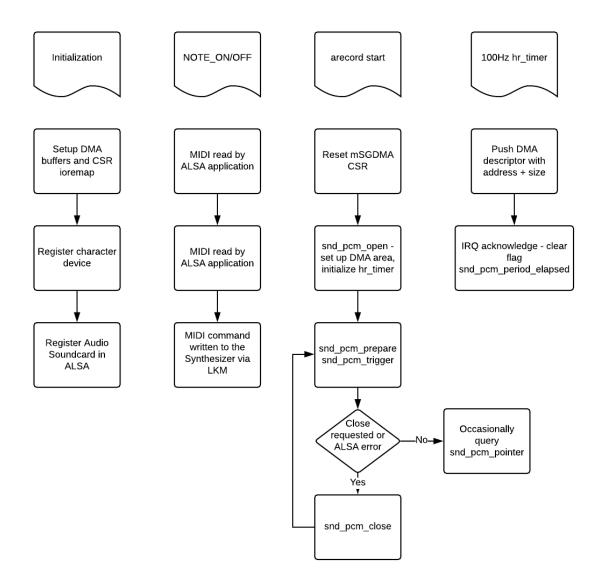

## 5. Software Design

The software part of the project comprises most importantly the Linux OS which was configured to support MIDI, ALSA, and JACK. Additionally, two main parts can be distinguished: MIDI decoder userspace application and a special Linux kernel driver to support receiving DMA buffers and feeding them to the ALSA system. Configuration of the system plays a major role in making this possible and is also described in much detail. Since the FPGA is a real device, it has to be recognized by the operating system and registered with the Linux platform system by a special driver. Even though there is much common knowledge regarding writing such a driver, fine-tuning communication parameters, and designing an efficient communication scheme proved to be demanding.

Figure 5.1. A software operation flowchart.

The logic flow of the software is visible in figure 5.1. Three major operating events

are visible: striking a MIDI note, commencing recording, and the high-resolution timer routine. It is worth mentioning that the recording logic flow is commenced by the arecord process and is regulated by ALSA, hence some function calls are subject to race conditions and in such places, a mutex is used to synchronize the concurrent access.

#### 5.1. Board Setup

First and foremost, since a special hardware device was created and had to be visible in the operating system, a new entry in the Device Tree Structure had to be populated. When the hardware design is completed, Quartus scripts can be utilized to generate the new DTS, which can be then provided to the bootloader and kernel. Next, the uBoot bootloader utilizes this DTS for itself and SPL generation so that proper hardware components are initialized at boot-time before Linux is loaded. Because some desired parameters and DTS entries are not properly exported by Quartus, they have to be moved manually - this is particularly relevant to custom clocks synthesized with the use of PLL's. Moreover, when designing custom IP cores, one has to export several parameters manually to a \_hw.tcl file, in order to add them to the generated DTS. Most of the commands and descriptions of this process in more detail can be found at dedicated wiki page[25] and thanks to quite dated but still valuable guide[26]. During the process of finding the proper and up-to-date way of setting up the board, I created a document summing up all these steps.[27]

Intel provides their own fork of Linux kernel - linux-socfpga[28], which is slightly modified to accommodate for some of their architectural differences and is lagging behind the development of the primary repository. Linux kernel version 4.14-130ltsi was used for this project as it was the latest version marked as long-term supported at the conception of this project. Apart from enabling ALSA support, ext4 filesystem, Loadable Kernel Modules, enabling FPGA Bridge and Manager, and setting the system type to Altera SOCFPGA Family no other changes are necessary in order to have kernel capable of working with this project.

The root filesystem used for this project was build using the Buildroot build system and needed only installing desired ALSA-lib applications such as aseqdump or arecord. In order to have a smooth project flow, I set up the Ethernet connection and transferred all necessary data via scp. There are few additional steps required for setting it up successfully, such as setting up sshd and generating enough entropy (which is scarce on embedded systems) with haveged. The scripts which perform these steps are available in the Appendices section with all other scripts.

When any Loadable Kernel Modules are built, they have to be installed to the target kernel manually by specifying it in the make command. Moreover, LKM have to be enabled in the target kernel in order to support them. With these steps completed, the initial SD card with the system image has to be flashed via a special utility script designed by Intel and available for download. The card has to be only reflashed when a change to the kernel or bootloader is required, any other change made to the rootfs can be made via Ethernet.

#### 5.2. MIDI receiving application

This is the first component that starts the processing chain, here the MIDI command is read from the ALSA system where it is provided by built-in ALSA kernel MIDI driver which supports the Launchpad keyboard. The command is decoded and reformatted to suit the internal format of messages for the FPGA synthesizer. Once formatted, it is written to the character device file of the memory-mapped Avalon Slave and received on the Hardware side. It supports the following events: NOTE\_ON, NOTE\_OFF, WAVE\_CHANGE, and a special command for turning off all the notes at once. The application supports reading on different MIDI ports, thus can be easily extended to support additional devices if the hardware allows for more USB connections or virtual MIDI generators.

The feeder application is paired with a kernel module whose only responsibility is the registration of the device file in sysfs and allowing writing into it, in turn transmitting the command to the FPGA. It writes on a word basis every time the userspace requests a write and the device is successfully registered.

Table 5.1. MIDI userspace command

| Bits     | 32 - 16 | 15     | 14-8      | 7-0      |  |  |

|----------|---------|--------|-----------|----------|--|--|

| Function | Unused  | ON/OFF | MIDI note | velocity |  |  |

The API used in this case is a simple *write* syscall which writes a single 32-bit word with a command composed of a truncated MIDI command visible in the table 5.1.

#### 5.3. DMA - ALSA synthesizer driver

Once the data is synthesized at the FPGA side, it is then sampled with a clock running at 96 kHz and submitted to the mSGDMA for transfer to the Linux driver. It is responsible for registering a soundcard within the ALSA system and performing DMA transactions for the data from the FPGA. When the application uses ALSA API for recording this data it uses a ring buffer, hence the driver has to follow the same fashion and allow for enough buffers so that buffer overruns do not occur. Each time a transaction is completed, an interrupt is fired from the DMA controller and the driver responds by informing ALSA that a recording period has elapsed. Because ALSA mostly uses a 'frame' terminology, which stands for one sample size taking into account the number of channels and data width, conversions from bytes are required. The format used is S32\_LE which is a 32-bit value, as the recorded file memory sizes are not of much relevance and this way the communication is faster. Even though the signal is 24-bit Little Endian it is stored as a 32-bit value, because of that, it can be played by most of the common audio players like VLC or Audacity.

At the time of writing this paper, the driver performs interrupts every 10ms thus requiring a high-resolution Linux clock, otherwise, jitter and stalling occur heavily disturbing the driver output. The device is controlled with special registers that are memory-mapped and controlled with control words.

#### 5.4. Obtaining the data

The userspace can make use of the data that the soundcard receives and for example use a program like arecord or audacity to capture its output. Currently, just a single format and sampling frequency is supported, which is caused by these parameters being fixed at the Hardware side. The data is also monophonic but multiple channels can be added as an extension, this would require support from the hardware side to either output the data in an interleaved format or in any other. Because the ext4 system in conjunction with the SD card is incapable of real-time audio processing, the recorded file is first saved to RAM in /tmp/ and then moved to the regular SD card.

## 6. Testing

Testing a system, especially a complex one, requires particular attention to detail throughout the whole design process. Starting from a simple Verilog module or a C language function, through independent testing of PL and the Linux kernel driver, to holistic system tests covering the whole project. While hardware can be tested with the help of standardized Verilog test benches and then plotted in ModelSIM, some parts have to be tested in ingenious ways. One such part is the DMA communication and observing the actual output from the 1 pin GPIO DAC. In this chapter are presented various methods used throughout the project to assess whether it meets the requirements.

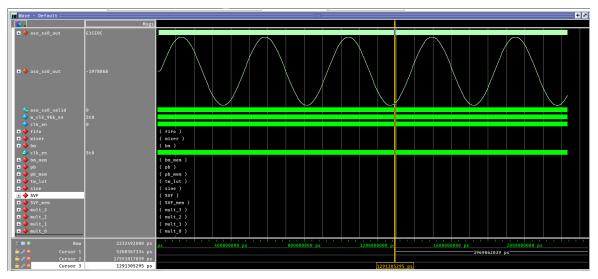

#### 6.1. Verilog Testbenches

The test-bench setup tested only the internals of the system, not the Avalon-MM and Avalon-ST external communication protocols because simulating them by hand would be very time-consuming. The ModelSIM simulation software was used to display the signals changing in time and to properly observe, understand, and then fix the faulty logic. Because two distinct clock domains are crossed in this project, debugging it proved to be quite challenging, especially with the SignalTap software, which requires onboard memory for storing real samples of current-cycle logic.

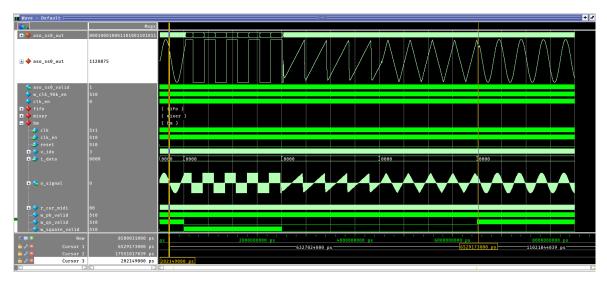

Figure 6.1. ModelSIM simulation view of E4 note.

A view of ModelSIM simulation waveforms can be found in figure 6.1.

Each component was tested using a test-bench setup containing all the necessary components, and short-circuiting the pipeline whenever one of them was not being tested. This in turn allowed for testing more complex scenarios, like turning notes on 1 by 1, or displaying all pipelined values simultaneously. This allowed for quick elimination of some rudimentary issues and testing whether the logic was proper. Unfortunately, ModelSIM

cannot behave equally to the real hardware, hence some errors slipped through this phase of testing. Most prominent of them are uninitialized variables, which ModelSIM initializes on its own and timing issues, especially with the double-clocking.

After testing in this fashion the device was programmed using SignalTap and proof checked whether simulated values occur on the device. Long compilation times and much more complex user controls did not appeal to me. Hence, I tested in this fashion only to observe whether something is occurring and debugged the logic back again in the simulator. SignalTap allows for quick reflashing of the debugging FPGA code using a JTAG connection. Once the PL behaved as predicted it could be flashed as .rbf into the SD card image.

Figure 6.2. ModelSIM simulation of all 4 waveforms.

Some additional results of the ModelSIM displaying various waveforms are visible in 6.2.

#### 6.2. Oscilloscope testing

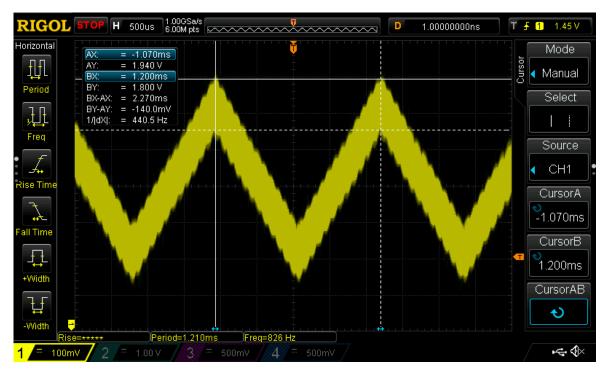

The 1 pin GPIO connection was utilized to output the signal to an RC circuit which then filtered out most high-frequency components that may appear in the spectrum. Even though the signal is perfectly audible in the headphones connected by the audiojack, and the RC components were chosen to provide cutoff frequency of 15,9kHz, not all noise was filtered out. After spending much time trying to achieve as noise-free signal as possible, I deduced what might be the cause of these noises - a DC-DC step-down converter(LTC3612), which operates at 4MHz. The periodic noise and its amplitude is visible in figure 6.3. Moving the RC circuit closer and further from the DC-DC converter aligns with my speculations, when closer the amplitude of the noise is much larger, when further it remains around 140mV. The headphone connection allowed for checking whether the sound being generated actually matches the MIDI note. Testing this way allowed

Figure 6.3. Periodic noise of 4MHz frequency.

to fine-tune the Tuning Word table and discover previously undiscovered errors in the project, effectively shifting MIDI notes back to their proper octaves.

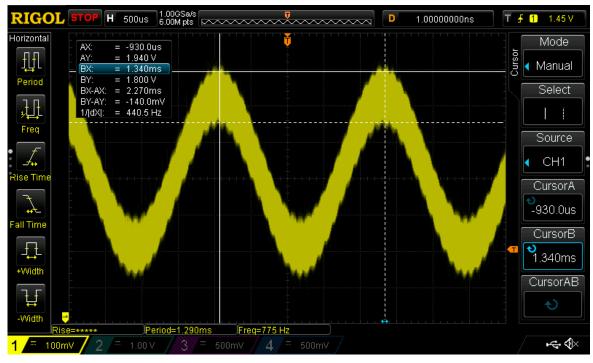

Figure 6.4. Sine wave DDS waveform for 440Hz

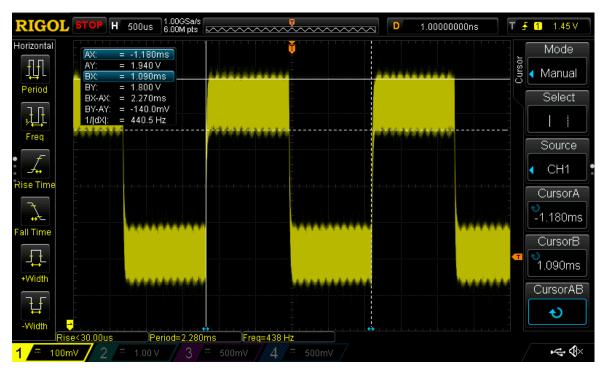

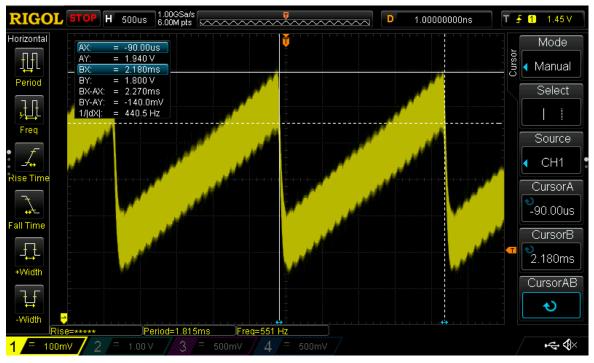

Figures 6.4 - 6.7 show sine, square, sawtooth and triangle waveforms the note A4 - MIDI 69 - 440Hz. As mentioned above, it is not filtered out completely, nevertheless, the

Figure 6.5. Square wave DDS waveform for 440Hz

Figure 6.6. Sawtooth wave DDS waveform for 440Hz

shape is visible. All the notes have corresponding recordings available in the .wav format for the reception. Although the DAC worked with the clock 100MHz, and the signal was measured at the output of Lowpass RC circuit, the output was still not free of noise. This

Figure 6.7. Triangle wave DDS waveform for 440Hz

quasi-periodic oscillation not filtered by the RC circuit is of about 10MHz periodicity which does not hint at any reasonable noise source.

#### 6.3. System Testing

Testing software was performed in a left-to-right approach - following the input signal, first testing the MIDI receiver, then the control kernel driver, finally testing the receiving kernel driver, and assessing whether the obtained result is as expected. Testing the ALSA MIDI application was actually quite simple, pressing different MIDI notes and observing what the output is. Some care had to be taken when composing the control word for the kernel driver, as not all MIDI fields were used. The control kernel driver, being as simple as possible was tested by observing whether the proper values appeared on the SignalTap output.

The most difficult part of the testing was the combined DMA driver and ALSA soundcard because of a lack of proper documentation and a tedious testing procedure. Testing was again performed in conjunction with SignalTap software to observe whether any values were being fed to the mSGDMA FIFO and then observing these values on the receiving side. The procedure was as follows:

- 1. Start recording with the arecord command on Linux side

- 2. Press Launchkey keys to generate NOTE\_ON's

- 3. Terminate the recording and copy the .wav file using scp to the host

- 4. Play the recording with aplay to observe whether it matches the one heard by the headphones connected to the DAC

- 5. Perform a hex dump of the .wav file with xxd

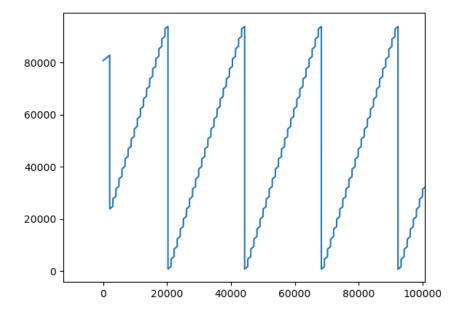

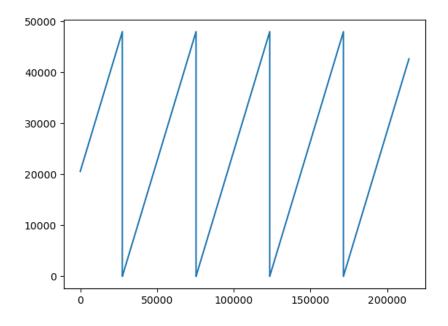

- 6. Plot the hex data using a python script and observe the waveform (performing endian conversion)

Choosing the proper parameters for ALSA soundcard and DMA buffer sizes was probably the most tedious task and in order to check whether the DMA communication was proceeding without any hiccups a special debug counter was input to the mSGDMA. Plotting of the values received by such deterministic testing rapidly pinpointed any problems. Choosing a proper ALSA encoding was also cumbersome, as with S24\_LE the signal appeared to sound almost proper, but when multiple notes were pressed only noise was audible. Changing the format to full 32-bits S32\_LE solved the problem and moreover allowed to playback this .wav file in every major music player.

Moreover, as discussed in the previous section, a problem I could not debug until the very end was ALSA overruns which were due to too slow ext4 filesystem. Changing the filesystem to tmpfs alleviated this instantly.

**Figure 6.8.** Visible jumps on the rising slope of the sawtooth. Caused by wrong DMA transfers window (ALSA period) size.

Two figures showing how DMA period size influences the continuity of the waveform are visible in 6.8 and 6.9.

With proper logs set up and mSGDMA Control Status Register being printed out, all issues with communication with the device were found out and solved. For the first testing

Figure 6.9. Proper continuous sawtooth.

of this communication a special userspace program was written, which would interface the mSGDMA as a character file and read from it in chunks of data.

## 6.3.1. Examples

Apart from the examples of every waveform being played at a frequency of 440Hz additional examples are necessary to prove that the system behaves as properly. In the file progression.wav one octave of progression may be heard starting from note C4 to C5 and one octave lower and higher in their respective recordings. Additionally, several tracks displaying the polyphonic abilities of the system are presented. Because the samples are mixed, their amplitude has to be reduced (by effectively dividing the sample in half or more), because of that notes played together sound louder than the single notes. Some additional examples are provided, such as very low frequency notes and very high frequency notes playback for a chosen wave-form.

Figure 6.10. Audacity output of an audio recording.

In figure 6.10 an Audacity output of the recorded file may be viewed. Distinct notes being pressed are visible, as well as periods of silence.

### 6.4. Debugging

Debugging such a complex system requires assessing what the key data is and how much of it should we monitor. Therefore, in PL special counter variables were introduced and plotted in the resulting ModelSIM simulation in order to assess which sample the module is currently processing. Without such facilitation debugging a pipelined architecture would be a hefty task.

Analyzing kernel Oopses was also insightful to debug undocumented ALSA code which misbehaved. Proper logging and logging levels were indispensable in debugging all issues in the kernel driver. Without both ALSA and ALSA-lib (arecord and aplay) source code, it would have been almost impossible to orient oneself in the error messages these libraries outputted.

### 6.5. Timing and Delays

Since this project is meant to be highly accurate and with minimal delays, proper choices of clocks and timing domains were essential. There are multiple choke-points that incur delays and these are discussed in more detail in this chapter. Most notable of which are: MIDI command input reading and dispatching, generating the DDS sample, and DMA data transfer.

### 6.5.1. Software delays

The delays in the software are minuscule and can only be alleviated with the usage of RT patched kernel or tweaking some scheduler related settings. Nevertheless, browsing through audio forums I decided it is not worth changing the default settings. Delays that I directly measured and modified were in the DMA driver, and these had a major impact on the quality of the recorded audio file. Starting from normal low-resolution Linux kernel timers, I could observe various delays and non-deterministic interrupts being generated due to the low accuracy of these timers. Replacing them with high-resolution timers reduced the issue, and as mentioned in subsectionSystem Testing the last glitches and delays were removed by the usage of tmpfs instead of ext4.

### 6.5.2. Hardware delays

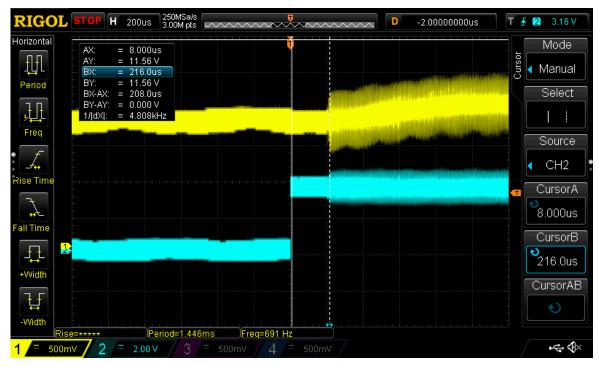

Contrary to software delays, hardware delays were almost wholly reducible by accurate programming and careful control of enabling signals. In the table 6.1. Because some signals may be generated in fewer number of cycles than other, the delay measured on the oscilloscope corresponds to the sinewave generation. It is visible that the delays are marginal and due to efficient filter choice and pipelining approach these delays will not grow very significantly if one decides to support more simultaneous samples generation. In figure 6.11 the measured delay between NOTE\_ON signal and start of waveform generation is measured. It can be observed that the delay is about 200 microseconds, which given a

| Step             | Delay (cycles) | Delay (ns) |

|------------------|----------------|------------|

| Acquire          | 2              | 20         |

| Phase increment  | 1              | 10         |

| Sine calculation | 4              | 40         |

| Filter           | 3              | 30         |

| Mixer            | 10             | 100        |

| Total delay:     | 20             | 200        |

Table 6.1. Synthesis delays

Figure 6.11. Delay between NOTE\_ON and the waveform being generated.

96kHz sampling rate amounts to about 20 samples delay, which at this sampling rate is minuscule. Because the sampling rate is much lower than the internal FPGA generation rate, these delays are mostly due to the internal sampling clock speed and not due to the generation process.

# 7. Results

High-quality sound output was achieved, slightly deteriorated on the analog side because of the usage of a single-bit Sigma-Delta DAC. However, the signal outputted via the ALSA driver meets the project requirements. As shown in the preceding paragraph, the delays are marginal and induced mostly by the software which does not work in real-time and is subject to the OS scheduler and priority degradation. In accordance with the project requirements, this delay is not audible and therefore acceptable. The possibility to playback up to 10 polyphonic sounds is possible, though the amplitudes of all the sounds have to be scaled in order to prevent overflows on the hardware side (which are of a too big magnitude to be in step with the mixer's amplitude-in-phase spreading possibilities). The system is thus portable and with a simple RC filter of even first order, the audio quality is decent and noiseless.

The sound can be recorded from the command line and then further processed if one wishes so. Moreover, it can be processed in real-time if the user wishes for it by means of connection to the ALSA soundcard this device emulates. Different waveform switching is also simple and non-intrusive to the sound being played. Because of this, fluent switching of the waveforms in a round-robin fashion is possible.

### 7.1. Resource Utilization

Although the De0-Nano-SoC is not a resource-rich platform, it provided even more than enough resources for a high-quality audio synthesis and filtering. Clever usage of LUTs and pipelining techniques allowed for hosting an efficient and effective system onboard. Because this was my first big SoC project, as mentioned before, I based my solution on the Grand Hardware Reference Design from Intel, which itself comprises some LE-heavy blocks. Some essential components, such as HPS-FPGA interconnections take up almost 25% of the board Logic Elements. With the SVF taking up almost half of the resources used by the synthesizer IP core, the rest is used mostly for the LUTs and registers required for pipelining. All the multipliers are offloaded to special DSP blocks which proved to be more than enough contrary to the initial doubts.

On the software side, the necessary components fit in a 512 MB SD card image and can be reduced even more if one desires so. The binaries are very small and the only limiting factor is the rootfs and kernel image size. However, because De0-Nano-SoC is quite formidable in terms of resources, I would consider even expanding the capabilities of kernel and rootfs with some onboard DSP or even adding an LCD and GUI to the synthesizer.

The resource utilization for this project is visible in 7.1. As mentioned above, the total usage of LE's is less than 50%, which contradicts initial doubts.

| Revision Name                   | soc system                   |

|---------------------------------|------------------------------|

|                                 |                              |

| Top-level Entity Name           | ghrd                         |

| Family                          | Cyclone V                    |

| Device                          | 5CSEMA4U23C6                 |

| Timing Models                   | Final                        |

| Logic utilization (in ALMs)     | 7,226 / 15,880 ( 46 % )      |

| Total registers                 | 9668                         |

| Total pins                      | 230 / 314 ( 73 % )           |

| Total virtual pins              | 0                            |

| Total block memory bits         | 604,032 / 2,764,800 ( 22 % ) |

| Total RAM Blocks                | 78 / 270 ( 29 % )            |

| Total DSP Blocks                | 19 / 84 ( 23 % )             |

| Total HSSI RX PCSs              | 0                            |

| Total HSSI PMA RX Deserializers | 0                            |

| Total HSSI TX PCSs              | 0                            |

| Total HSSI PMA TX Serializers   | 0                            |

| Total PLLs                      | 1 / 5 ( 20 % )               |

| Total DLLs                      | 1/4(25%)                     |

|                                 |                              |

Figure 7.1. Resource utilization for the project.

# 8. Conclusions

The project goals were successfully achieved, some were even surpassed and because of the way the project was structured, further, expansion is possible and uncomplicated. During the development of this project, I have learned about a variety of subjects, starting from resolving and debugging hardware issues, through digital signal processing topics to finish on Linux device drivers and ALSA architecture understanding. The knowledge gained in these areas will surely allow me to expand upon this project and approach even more complex systems with more ease.